02:34 PM بتوقيت شرق الولايات المتحدة – أعلنت Xilinx ، الشركة المصنعة لـ FPGAs ، عن محرك Versal AI الجديد العام الماضي كوسيلة لنقل FPGAs إلى مجال AI. تم تعيين هذا الكلام للتوسع في هذه الإعلانات.

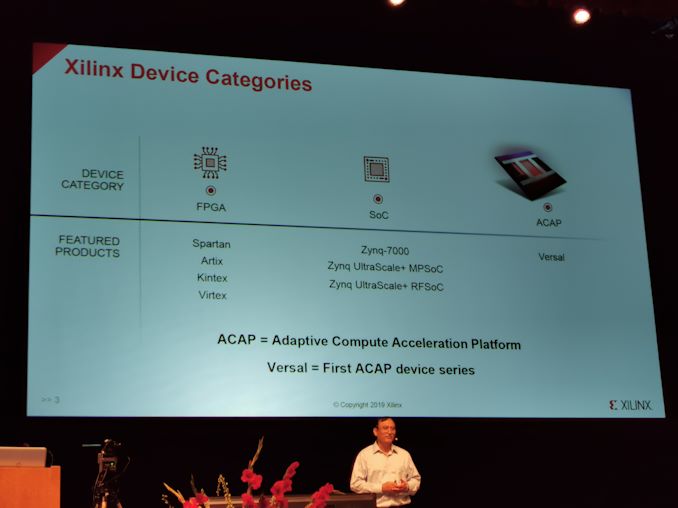

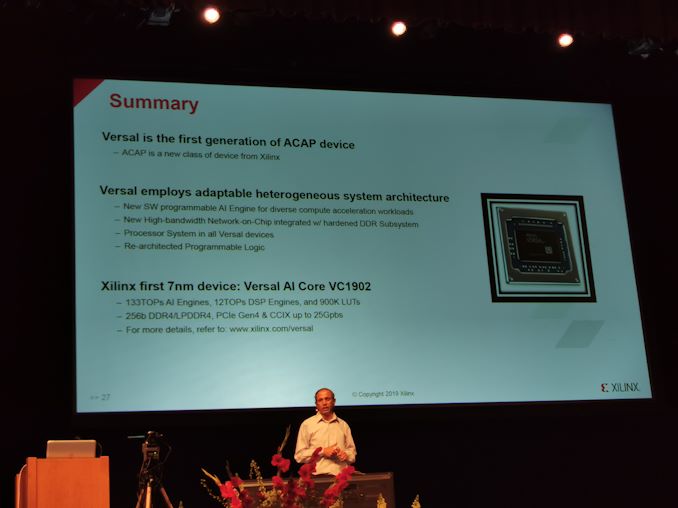

02:36 PM بتوقيت شرق الولايات المتحدة – فئات أجهزة Xilinx: FPGA و SoC و ACAP. Versal هو ACAP

02:37 PM بتوقيت شرق الولايات المتحدة – ACAP = النظام الأساسي لتسريع الحساب التكيفي

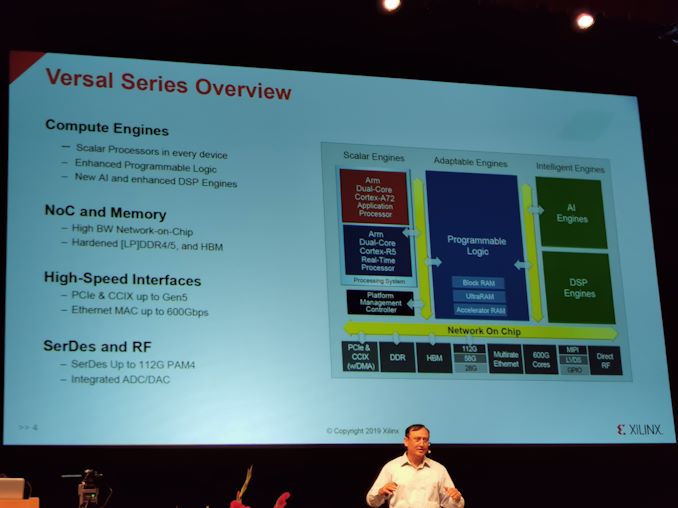

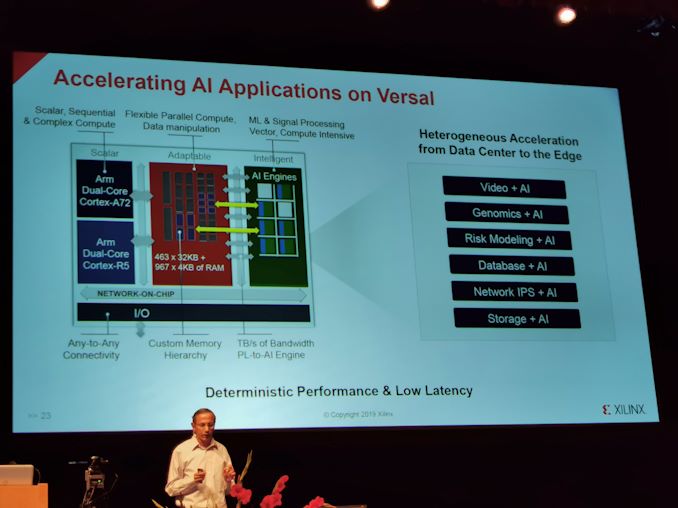

02:37 PM بتوقيت شرق الولايات المتحدة – المعالجات العددية ، والمنطق القابل للبرمجة ، ومحركات AI / DSP ، والشبكات على متن الطائرة

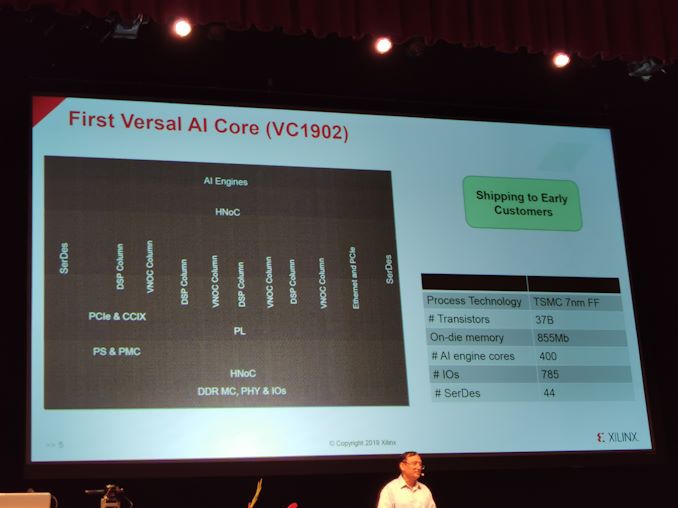

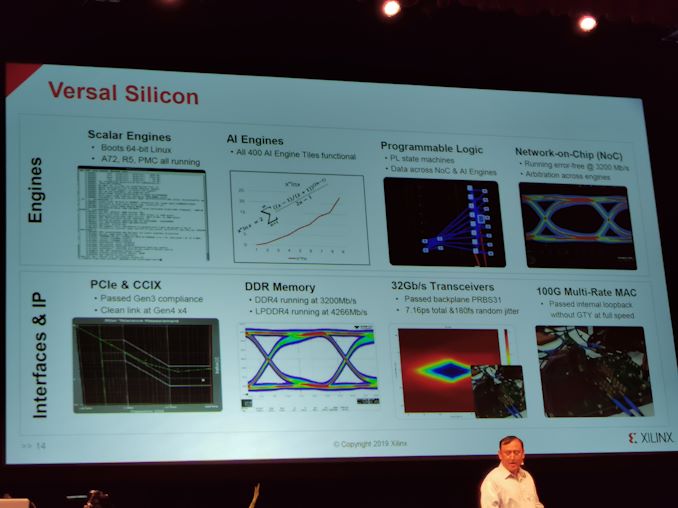

02:38 PM بتوقيت شرق الولايات المتحدة – حاليا شحن العينات للعملاء في وقت مبكر

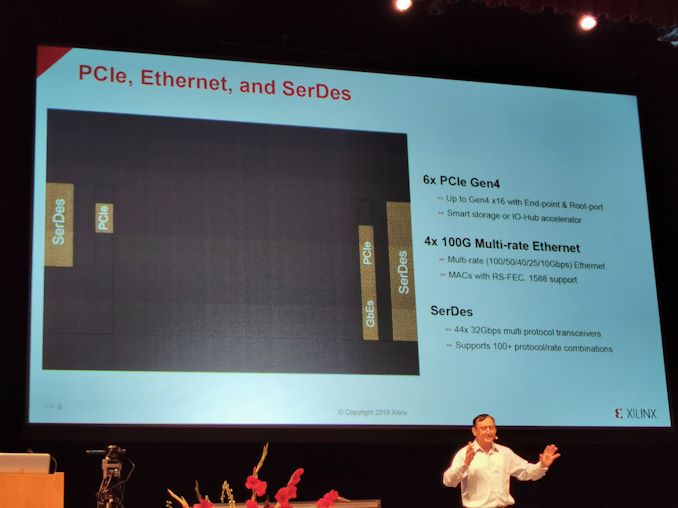

02:38 PM بتوقيت شرق الولايات المتحدة – TSMC 7nm ، ترانزستورات 37B ، 855 ميجابايت على الذاكرة ، 400 محرك قلب ، 785 IOs ، 44 SerDes

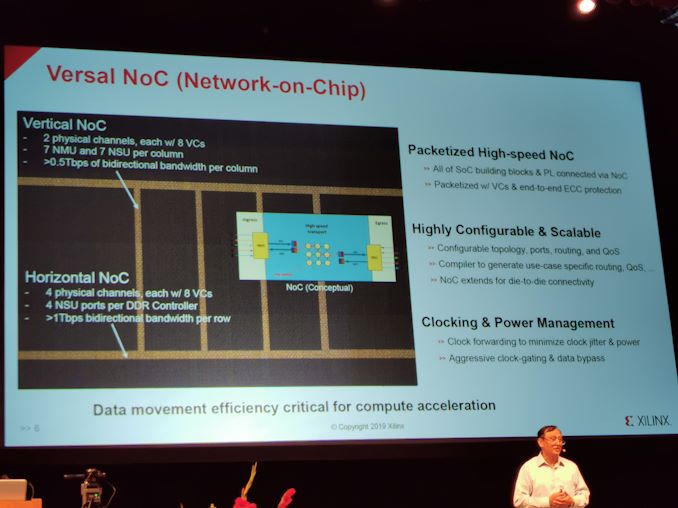

02:39 PM بتوقيت شرق الولايات المتحدة – Versal NOC – NOC العمودي و NOC الأفقي

02:39 PM بتوقيت شرق الولايات المتحدة – NOC packetized ، على مدار الساعة العدوانية النابضة

02:40 PM بتوقيت شرق الولايات المتحدة -> 1 تيرابايت في الثانية عرض النطاق الترددي ثنائي الاتجاه لكل صف ،> 0.5 تيرا بايت في الثانية عرض النطاق الترددي ثنائي الاتجاه لكل عمود

02:40 PM بتوقيت شرق الولايات المتحدة – لديك دائما قنوات افتراضية في NOC

02:40 PM بتوقيت شرق الولايات المتحدة – تسارع حساب هو كل شيء عن حركة البيانات

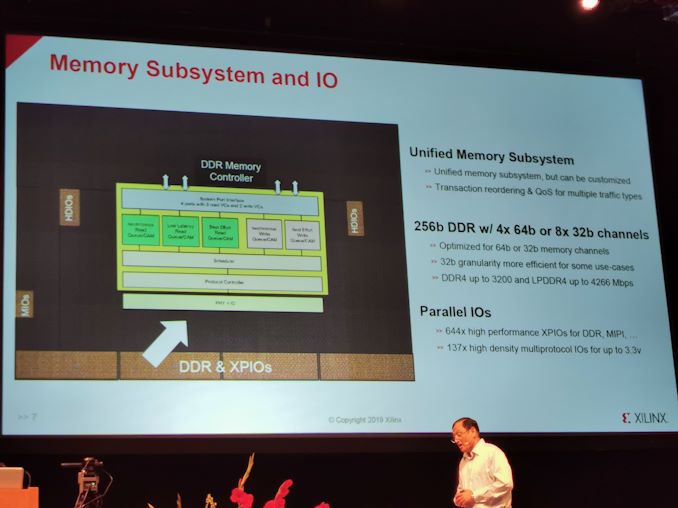

02:41 PM بتوقيت شرق الولايات المتحدة – النظام الموحد للذاكرة الفرعية

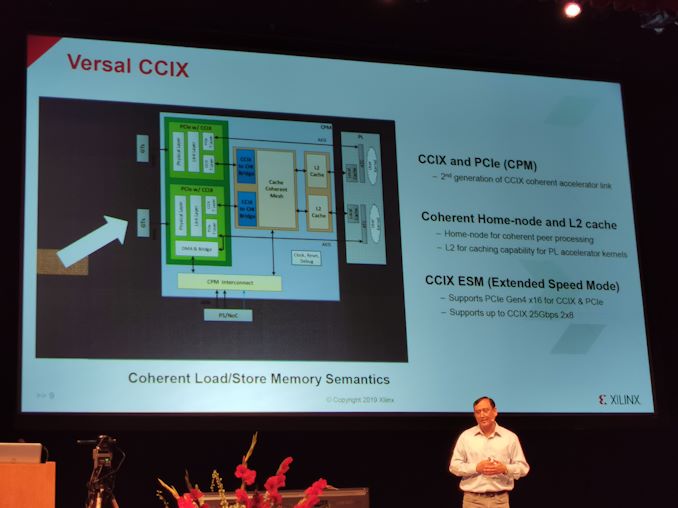

02:43 PM بتوقيت شرق الولايات المتحدة – 2nd الجنرال CCIX

02:44 PM بتوقيت شرق الولايات المتحدة – عقدة متماسكة الرئيسية ، وذاكرة التخزين المؤقت L2

02:45 PM بتوقيت شرق الولايات المتحدة – CCIX ESM – يدعم PCIe Gen 5 x16

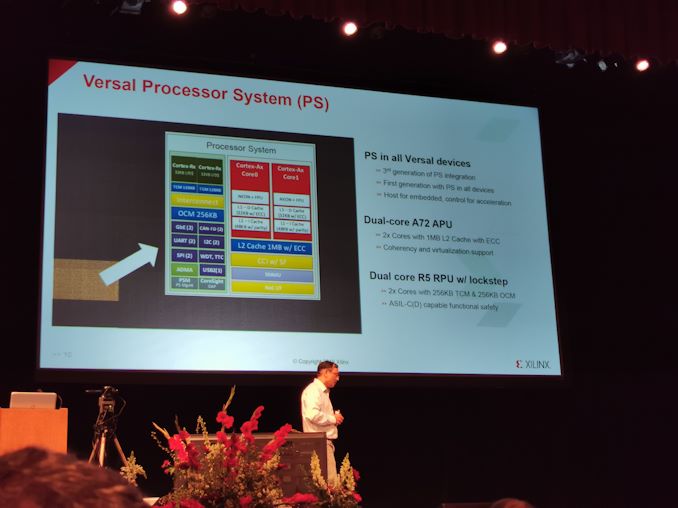

02:45 PM بتوقيت شرق الولايات المتحدة – نظام معالج Versal

02:45 PM بتوقيت شرق الولايات المتحدة – في جميع الأجهزة Versal

02:46 PM بتوقيت شرق الولايات المتحدة – ثنائي النواة a72

02:46 PM بتوقيت شرق الولايات المتحدة – ثنائي النواة R5 RPU ث / locksetp

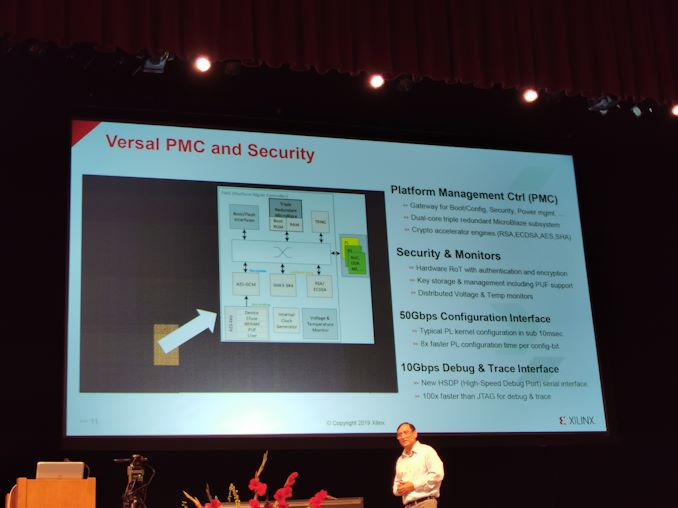

02:46 PM بتوقيت شرق الولايات المتحدة – التحكم في إدارة المنصة

02:47 PM بتوقيت شرق الولايات المتحدة – مسرعات تشفير للأمن

02:47 PM بتوقيت شرق الولايات المتحدة – 10 جيجابت في الثانية تصحيح الأخطاء واجهة التتبع

02:48 PM بتوقيت شرق الولايات المتحدة – 50 جيجابت في الثانية واجهة التكوين

02:48 PM بتوقيت شرق الولايات المتحدة – الأجهزة RoT

02:48 PM بتوقيت شرق الولايات المتحدة – محرك SHA3 ، AES ، RSA ، مفتاح AES

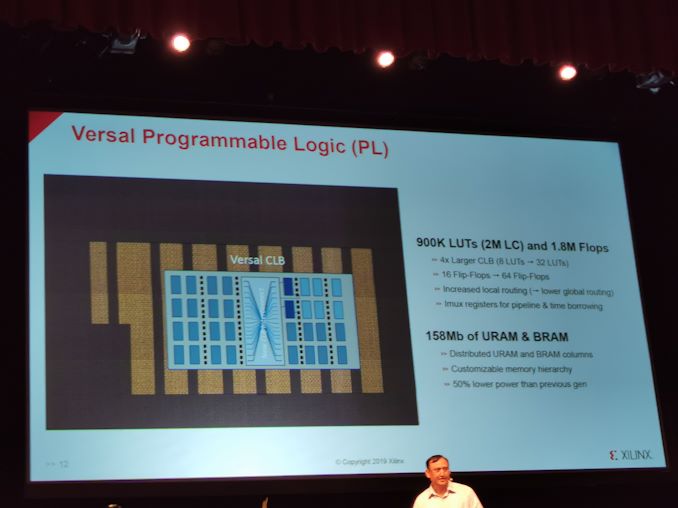

02:48 PM بتوقيت شرق الولايات المتحدة – المنطق القابل للبرمجة – 900K LUTs ، 2M LC ، و 1.8 M FLOPs

02:48 PM بتوقيت شرق الولايات المتحدة – 4x أكبر CLB -> 64 يتخبط

02:48 PM بتوقيت شرق الولايات المتحدة – 158 ميجا بايت من URAM و BRAM – طاقة أقل بنسبة 50٪ من السابق

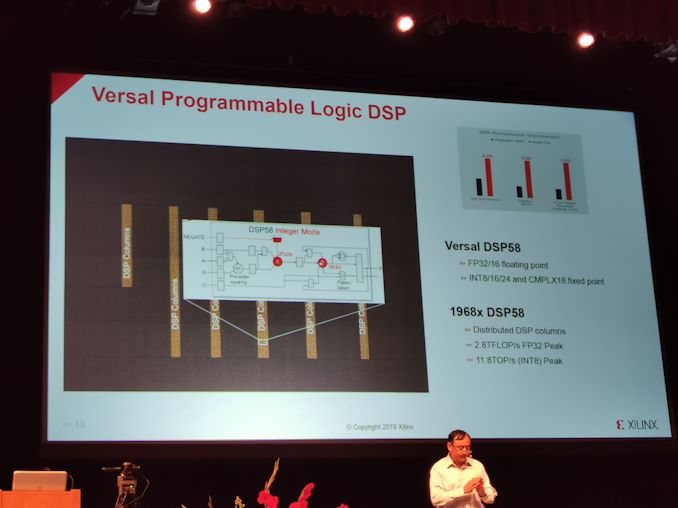

02:48 PM بتوقيت شرق الولايات المتحدة – Versal برمجة المنطق DSP ، DSP58

02:48 PM بتوقيت شرق الولايات المتحدة – 1958x DSP58 بدعم FP

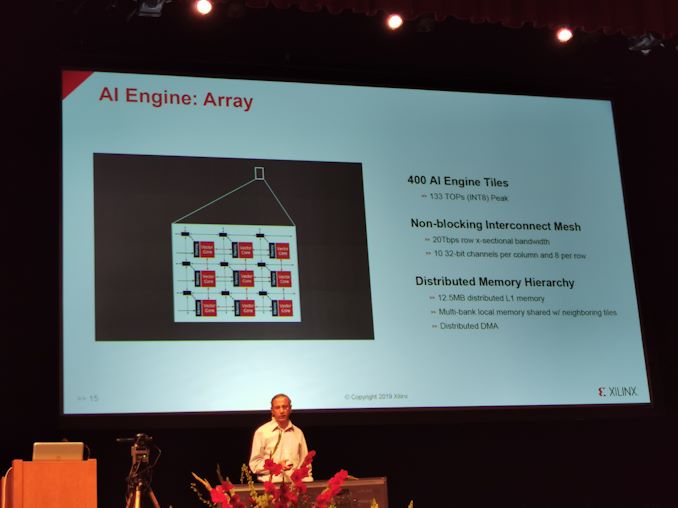

02:49 PM بتوقيت شرق الولايات المتحدة – 400 AI بلاط المحرك ، 133 قمم في INT8

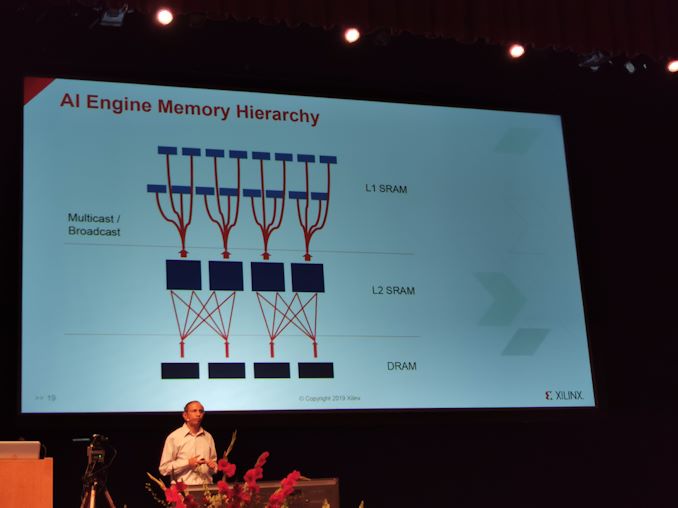

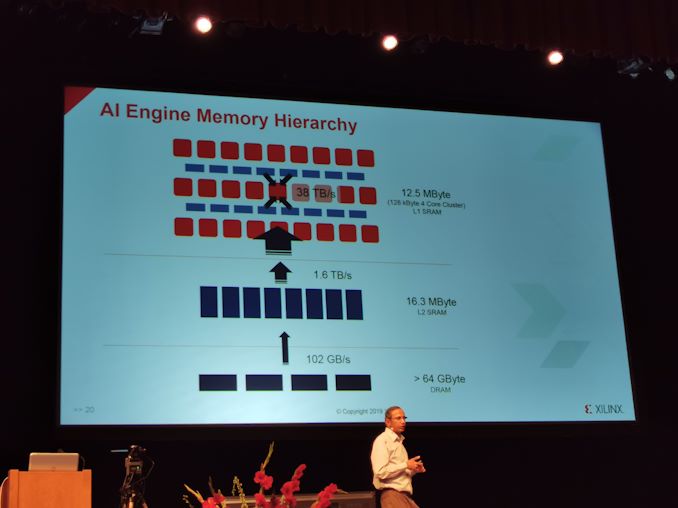

02:49 PM بتوقيت شرق الولايات المتحدة – عدم ربط شبكة الربط

02:49 PM بتوقيت شرق الولايات المتحدة – 12.5 ميجابايت من ذاكرة L1 الموزعة

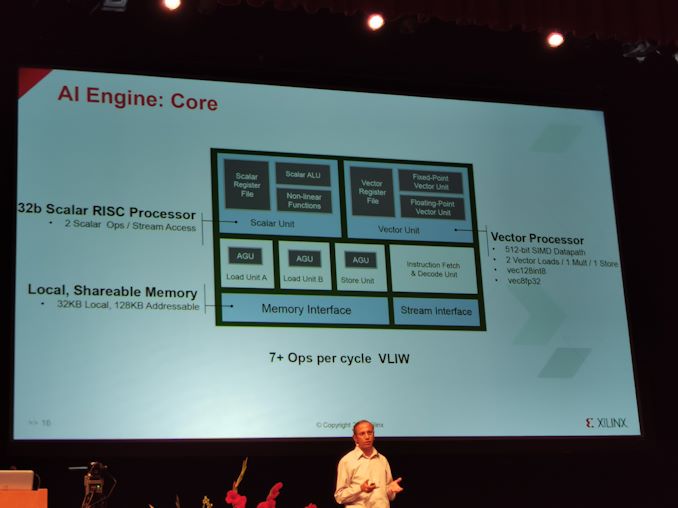

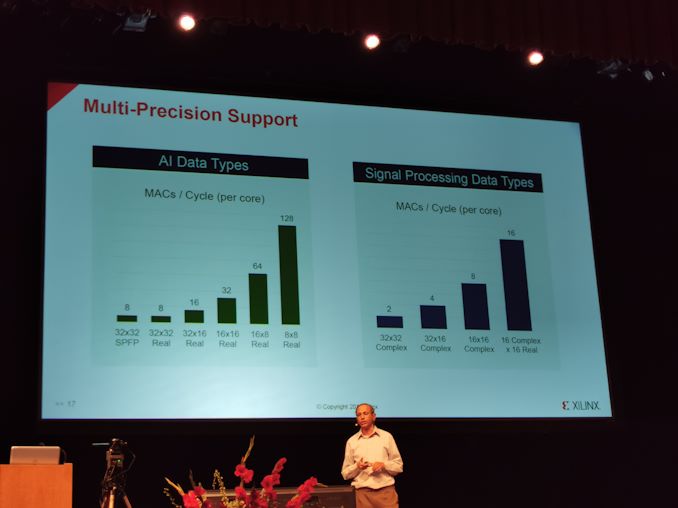

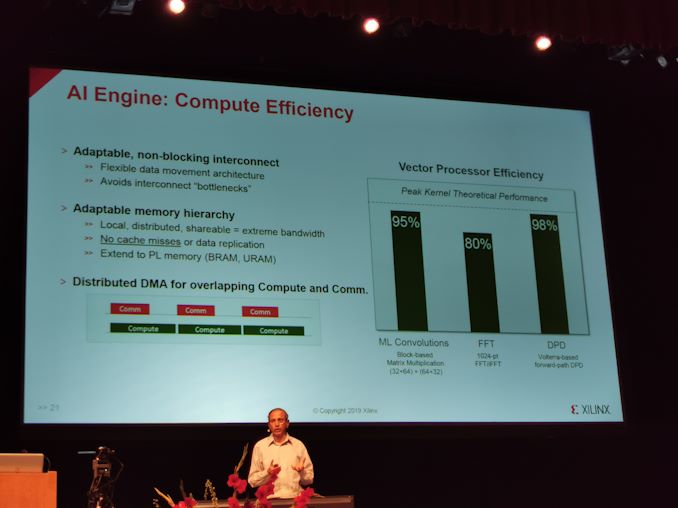

02:51 PM بتوقيت شرق الولايات المتحدة – في محرك AI: معالج Scalar RISC 32b ، و 2 ops / دفق وصول قياسي ، معالج 512 بت متجه SIMD ، vec128int8 أو vec8fp32 ، 7+ OPS لكل دورة VLIW

02:51 PM بتوقيت شرق الولايات المتحدة – 128 INT8 MACs لكل دورة لكل قلب

02:51 PM بتوقيت شرق الولايات المتحدة – مناسبة لأحمال العمل معالجة الإشارات

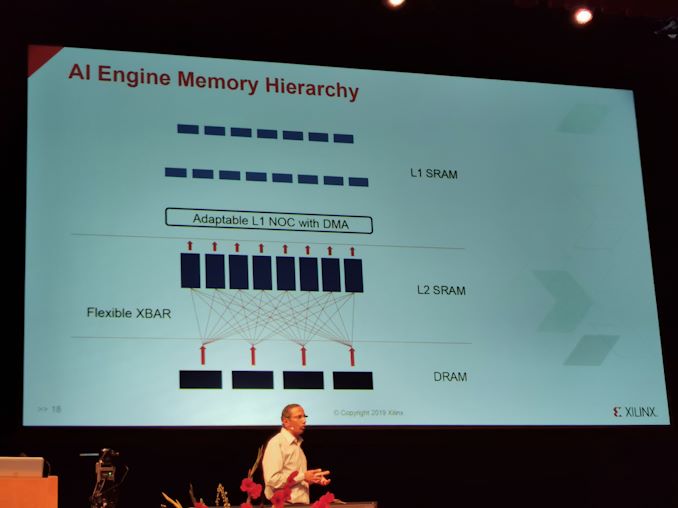

02:52 PM EDT – تتم حركة البيانات من خلال DMA المدبرة

02:53 PM بتوقيت شرق الولايات المتحدة – ذاكرة التخزين المؤقت يدعم البث / البث

02:53 PM بتوقيت شرق الولايات المتحدة – انتقال فعال جدا من البيانات المتدفقة

02:56 PM EDT – تقدم Versal أداءً حتمياً ووقت استجابة منخفض

02:56 PM EDT – خريطة حساب على أجزاء مختلفة من ACAP

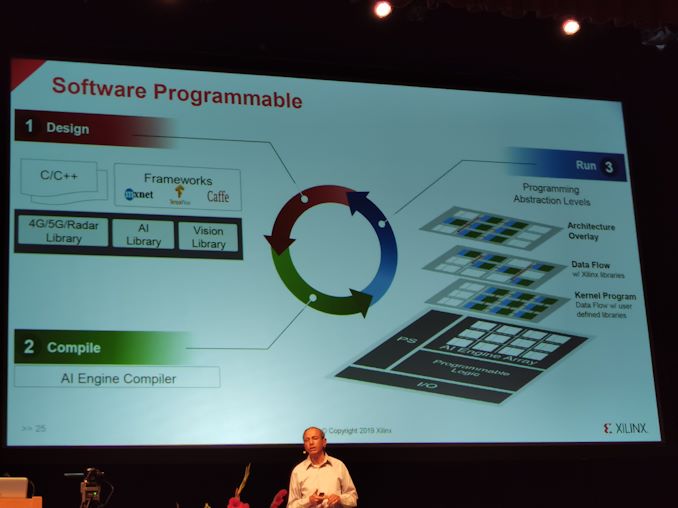

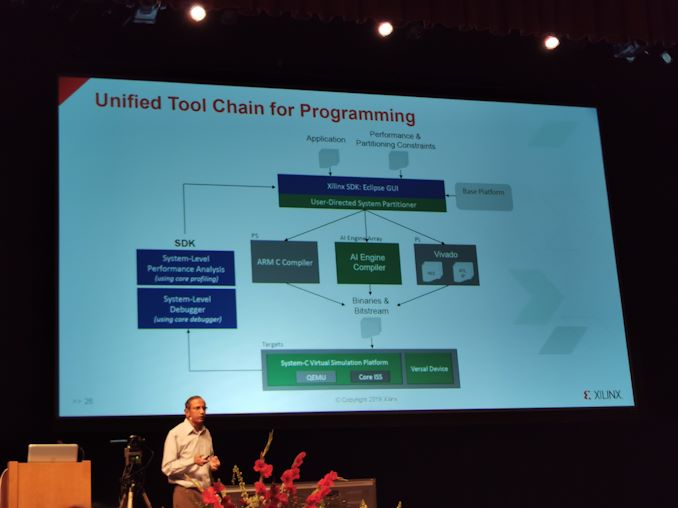

02:57 PM بتوقيت شرق الولايات المتحدة – برمجيات إطار قابل للبرمجة

02:58 PM بتوقيت شرق الولايات المتحدة – محاولة تجريد البرمجة من الأجهزة إلى C ++ العادية

02:58 PM بتوقيت شرق الولايات المتحدة – أطر مثل mxnet ، TensorFlow ، Caffee

02:59 مساءً بتوقيت شرق الولايات المتحدة – أول جهاز Xilinx 7nm و 133 TOP و PCIe Gen4 و CCIX

02:59 مساءً بتوقيت شرق الولايات المتحدة – بنية النظام غير المتجانسة القابلة للتكيف

03:00 مساءً بتوقيت شرق الولايات المتحدة – سؤال وجواب

03:00 مساءً بتوقيت شرق الولايات المتحدة – س: HBM؟ ج: قادمة

03:01 PM بتوقيت شرق الولايات المتحدة – س: دعم CCIX؟ دعم Gen-Z و CXL؟ أنت أعضاء في تلك الاتحادات. ج: لا توجد خطة رسمية بشأن الجنرال زي. CXL لا تزال جديدة.

03:01 PM بتوقيت شرق الولايات المتحدة – هذا هو التفاف. الحديث التالي هو إنتل سبرينغ كريست.